PL DRAM IP Drive Strength, ODT, and V REF Configuration Table 1: Supported PL DRAM Configurations Table 2 outlines the supported PS DRAM performance and configurations, PS DRAM configurations found in DS925, Configuration and Security Unit Performance Table. Table 1 outlines the supported PL DRAM configurations, PL DRAM performance, and configurations found in DS923, Maximum Physical Interface (PHY) Rate for Memory Interfaces Table.

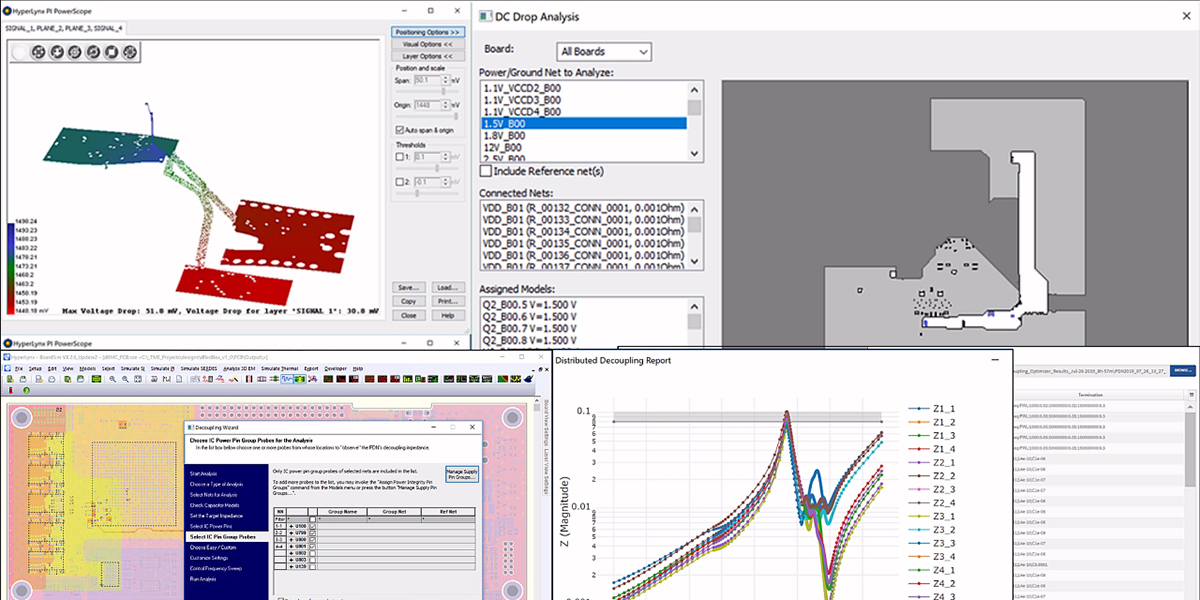

MPSoC devices support both PL and PS DRAM interfaces MPSoC, Processing System (PS), Configured with Processor Configuration Wizard (PCW) This chapter provides an overview of the supported DRAMs and configurations. The UltraScale and UltraScale+ families of FPGAs and MPSoCs support several different DRAM technologies and configurations. ODT and V REF configuration settings for each supported DRAM interfaceĪvailable resources for HyperLynx and ADS simulation tools This guide provides the following details and guidance The Custom IBIS models capture this information and can be used for board-level simulation. This information is captured in the sections below.

These values are used when the IP is generated. Xilinx has determined through extensive simulation and characterization, the FPGA and DRAM configuration settings including Drive Strength, ODT, and Vref.

#Hyperlynx fpga simulation how to

5.2.4 How to Generate Custom IBIS File for Zynq PS DDR.5.2.3 Creating a Custom PL IBIS File from an Implemented Design.5.2.2 Generate a custom PL IBIS File from the I/O Pin Planner.5.2.1 How to generate custom IBIS Files from Vivado.5.2 Vivado Generated, Custom IBIS Models.4.5 Manually finding the DRAM Configuration Settings.4 Zynq UltraScale+ MPSoC DDR Subsystem Drive Strength, ODT and V REF Configuration.3.5.2.2 Finding details in custom IBIS Model.3.5 Manually finding the DRAM Configuration Settings.3 PL DRAM IP Drive Strength, ODT, and V REF Configuration.

0 kommentar(er)

0 kommentar(er)